AVX-512, AMX, HBM2e 기능을 애드온 "유료 DLC" 기능으로 제공하는 Intel Sapphire Rapids-SP

| 출처 | https://www.hardwaretimes.com/intel-sapphire-rapids-sp-to-feature-avx-512-amx-hbm2e-features-as-add-on-paid-dlc-functions/ |

|---|

설마 CPU로 DLC장사를...ㅋㅋ

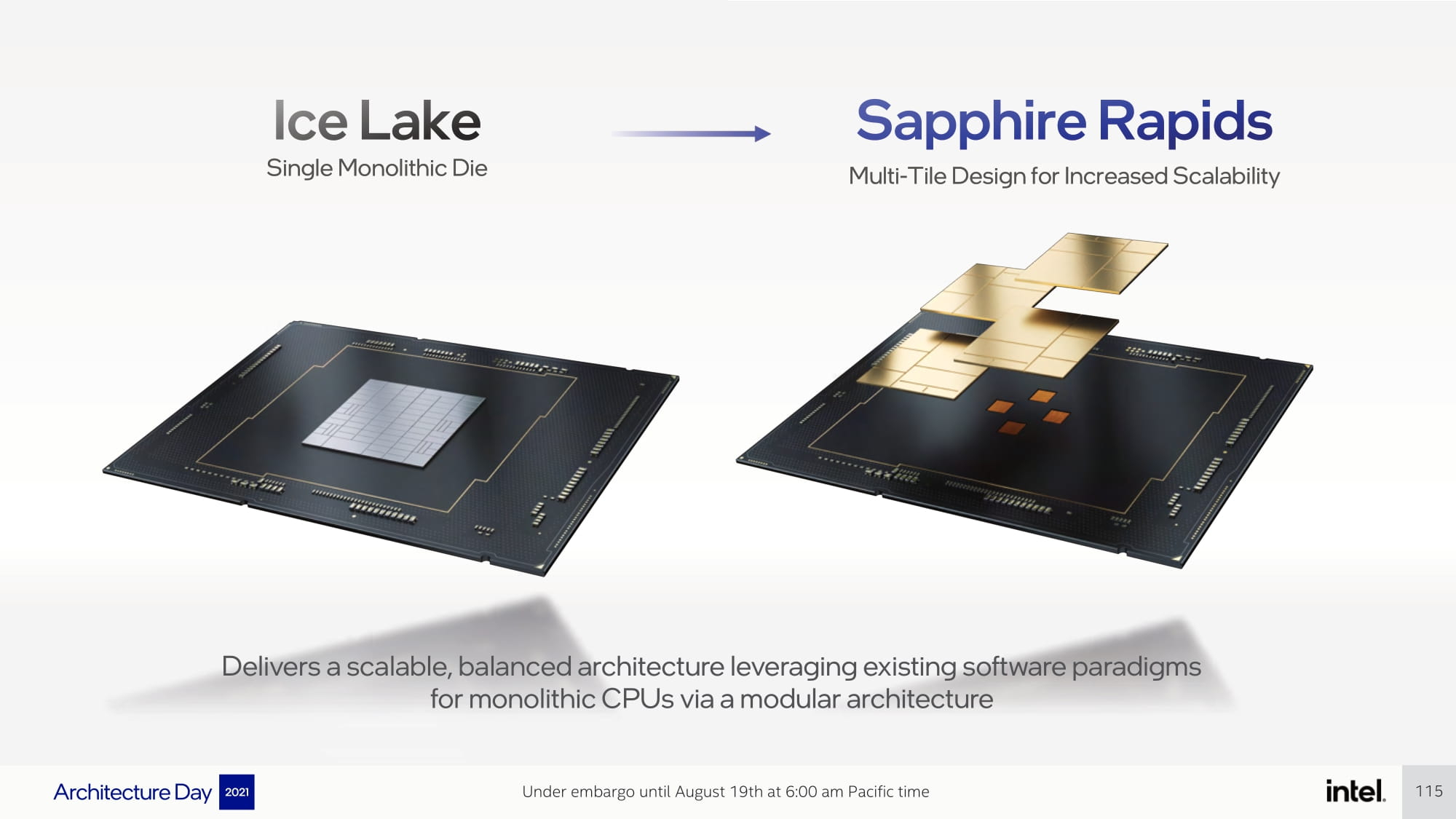

Intel은 강력한 Golden Cove 코어 아키텍처를 기반으로 올해 후반에 서버 및 HEDT 프로세서를 출시할 준비를 하고 있습니다. 코드명 Sapphire Rapids-SP인 4세대 Xeon Scalable 라인업 은 4개의 15코어 타일에 최대 56코어를 특징으로 하는 최초의 칩렛 (MCM 또는 타일, 원하는 대로 부름) 기반 설계가 될 것입니다. 각 다이에는 수율을 향상시키기 위해 융합된 하나의 코어가 있습니다. Ice Lake-SP와 마찬가지로 AVX-512 및 새로 추가된 AMX 명령은 AMD의 Epyc Milan, Milan-X 및 곧 출시될 Genoa 라인업에 대한 Intel의 주요 이점이 될 것입니다.

하지만 중요한 발견이 있었습니다. 인텔 은 비디오 게임의 유료 DLC와 마찬가지로 일종의 페이월 뒤에 AVX-512 및 AMX 명령을 제어할 예정 입니다. 소프트웨어 정의 실리콘 "SDSi"로 알려진 기능은 주로 Linux 커널을 통해 서버 및 데이터 센터 노드에서 활성화되어 공급업체가 가격에 특별한 "가속기" 또는 "추가 기능"을 클라이언트에 제공할 수 있습니다.

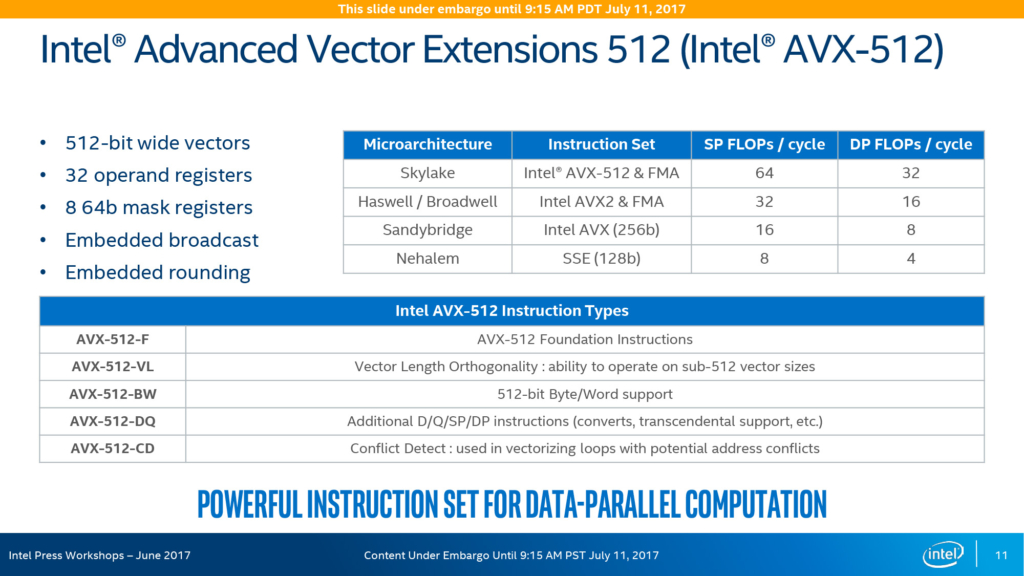

AVX-512는 주로 명령어가 밀집된 특정 데이터 센터 워크로드에서 활용 되므로 AVX2에 비해 실행 처리량을 두 배로 늘릴 수 있습니다. 단점은 많은 응용 프로그램이 AVX-512를 지원하지 않으며 지원하더라도 전력 소모가 크게 증가하는 대신 성능이 추가된다는 것입니다.

반면 AMX는 NVIDIA의 Tensor 코어와 유사하여 행렬 곱셈 및 기타 관련 2D 데이터 유형을 가속화합니다. 이들은 기본 파이프라인에 영향을 주지 않고 AVX-512 및 기타 기존 x86 명령어와 병렬로 실행됩니다.

출처(YuuKi_Ans)에 따르면 AVX-512 및 AMX 외에도 HBM2e 온다이 메모리의 특정 기능이 추가 기능이 될 것이라고 합니다. 우리는 이미 HBM 메모리가 기존 방식 외에도 플랫 모드 또는 캐시 모드에서 사용할 수 있다는 것을 알고 있습니다. 이러한 기능은 기본적으로 제공될 것입니다.

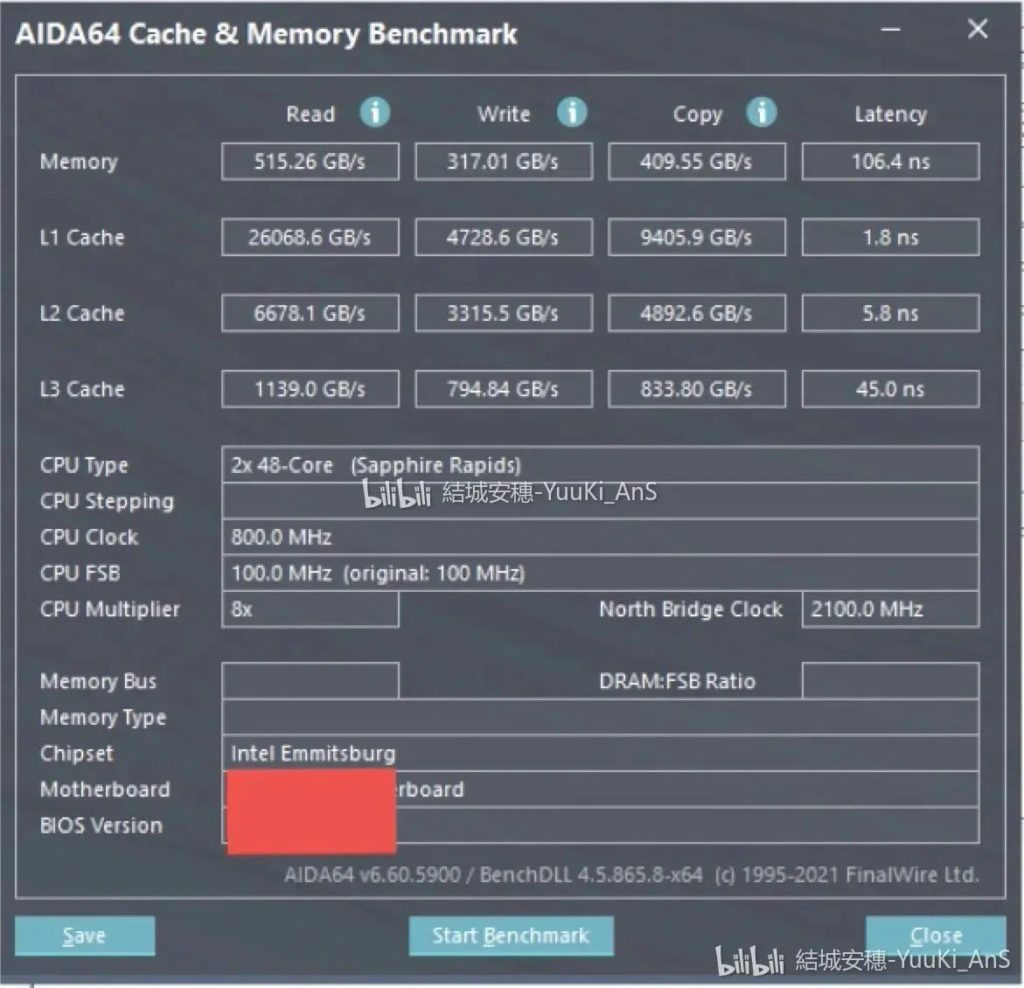

소스에서 공유한 샘플의 메모리 대기 시간을 보면 Intel이 메모리 대역폭을 대폭 강화하여 AMD의 Epyc Milan-X보다 (거의) 두 배, 이전 Ice Lake보다 50% 더 빨라진 것이 분명합니다. 이것이 더 빠른/더 큰 캐시의 결과인지 HBM2e 메모리가 포함된 결과인지는 확실하지 않습니다. 대기 시간이 전반적으로 타격을 입었지만 캐시에 대해서도 마찬가지입니다.