무어의 법칙은 살아있다: 인텔, 2030년까지 차세대 칩에 1조 개의 트랜지스터로 가는 길을 닦다

| 출처 | https://wccftech.com/moores-law-lives-on-intel-paves-way-to-a-trillion-transistors-in-next-gen-chips-by-2030/ |

|---|

결과물로 보여줬으면...

IEDM에서 인텔 리서치는 무어의 법칙이 어떻게 적용되는지, 그리고 Chipzilla 가 2030년까지 1조 개의 트랜지스터가 탑재된 차세대 칩을 어떻게 제공할 계획인지 보여주었습니다.

무어의 법칙에 힘을 실어 2030년까지 1조 개의 트랜지스터로 가는 길을 닦는 인텔 연구

보도 자료: 트랜지스터 75주년 기념일인 IEDM 2022에서 인텔은 패키징 기술에서 새로운 10배 밀도 향상을 목표로 하고 트랜지스터 스케일링을 개선하기 위해 단 3원자 두께의 새로운 재료를 사용합니다.

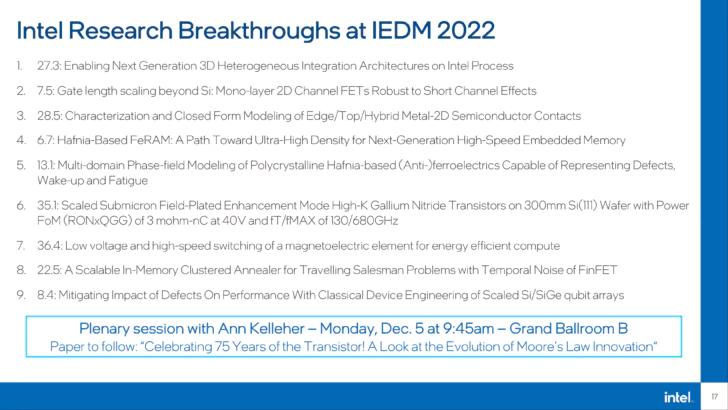

새로운 소식: 오늘 인텔은 향후 10년 동안 하나의 패키지에 1조 개의 트랜지스터에 대한 무어의 법칙을 유지하기 위한 혁신 파이프라인에 연료를 공급하는 연구 혁신을 발표했습니다. IEEE International Electron Devices Meeting(IEDM) 2022에서 인텔 연구원들은 밀도가 10배 향상된 새로운 3D 패키징 기술의 발전을 선보였습니다. 3 원자 두께의 초박형 재료를 포함하여 RibbonFET를 넘어서는 2D 트랜지스터 스케일링을 위한 새로운 재료; 고성능 컴퓨팅을 위한 에너지 효율성 및 메모리의 새로운 가능성; 양자 컴퓨팅을 위한 발전.

“트랜지스터가 발명된 지 75년이 지난 지금 무어의 법칙을 주도하는 혁신은 전 세계적으로 기하급수적으로 증가하는 컴퓨팅 수요를 지속적으로 해결하고 있습니다. IEDM 2022에서 인텔은 현재와 미래의 장벽을 허물고, 만족할 줄 모르는 수요를 충족하고, 무어의 법칙을 앞으로도 계속 유지하는 데 필요한 미래지향적이고 구체적인 연구 발전을 선보이고 있습니다.”

— Gary Patton, 인텔 부사장 겸 구성 요소 연구 및 설계 지원 총괄 책임자

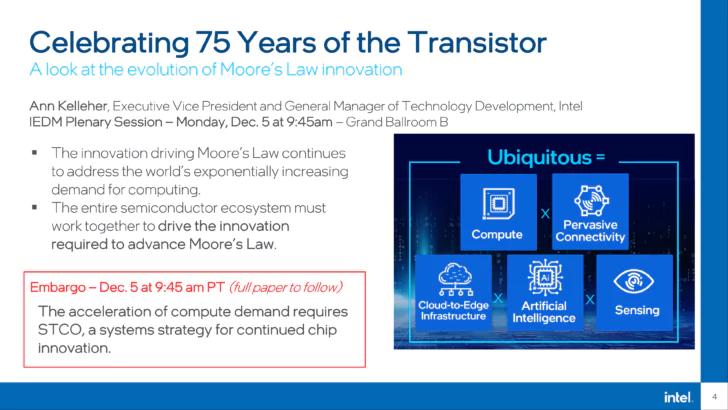

IEDM에서 일어나는 일: 트랜지스터의 75주년을 기념하여 인텔 부사장 겸 기술 개발 총책임자인 Ann Kelleher 박사가 IEDM에서 총회를 이끌 예정입니다. Kelleher는 컴퓨팅에 대한 세계의 증가하는 수요를 해결하고 무어의 법칙 속도로 발전하기 위해 보다 효과적으로 혁신하기 위해 시스템 기반 전략을 중심으로 생태계를 규합하는 지속적인 산업 혁신을 위한 경로를 설명합니다. 세션 "트랜지스터 75주년 기념! A Look at the Evolution of Moore's Law Innovation"은 12월 5일 월요일 PST 오전 9시 45분에 진행됩니다.

중요한 이유: 무어의 법칙은 급증하는 데이터 소비와 AI(인공 지능) 증가로 인해 수요가 가장 빠르게 증가함에 따라 전 세계의 만족할 줄 모르는 컴퓨팅 요구 사항을 해결하는 데 필수적입니다.

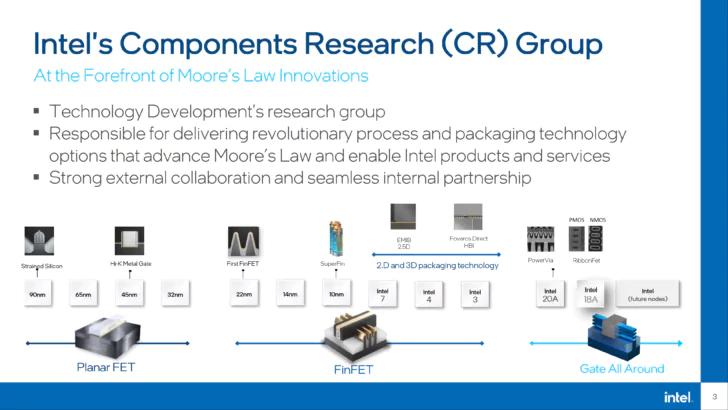

지속적인 혁신은 무어의 법칙의 초석입니다. 개인용 컴퓨터, 그래픽 프로세서 및 데이터 센터에서 스트레인드 실리콘, Hi-K 메탈 게이트 및 FinFET를 포함하여 지난 20년 동안 지속적인 전력, 성능 및 비용 개선을 위한 많은 주요 혁신 이정표는 Intel의 Components Research Group에서 시작되었습니다. . RibbonFET gate-all-around(GAA) 트랜지스터, PowerVia 후면 전원 공급 기술, EMIB 및 Foveros Direct와 같은 패키징 혁신을 포함한 추가 연구는 현재 로드맵에 있습니다.

IEDM 2022에서 인텔의 구성 요소 연구 그룹은 무어의 법칙을 지속하기 위해 세 가지 핵심 영역에서 혁신하겠다는 의지를 보여주었습니다. 단일 칩에 더 많은 트랜지스터를 장착할 수 있는 초박형 2D 재료; 고성능 컴퓨팅을 위한 에너지 효율성 및 메모리의 새로운 가능성.

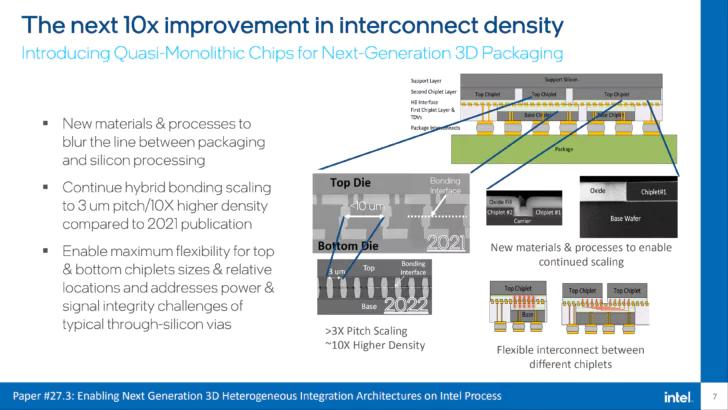

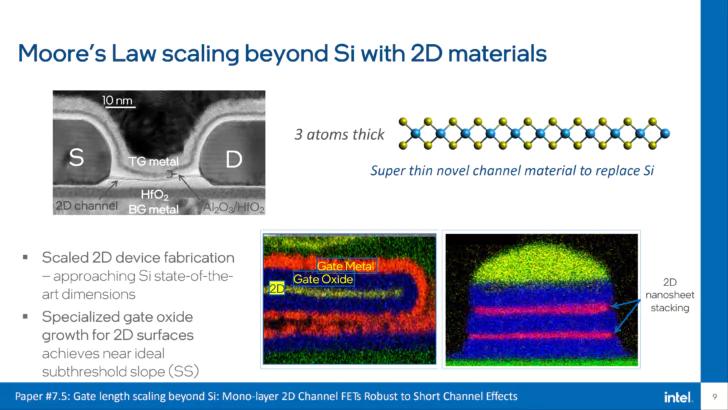

우리가 하는 일: Components Research Group 연구원들은 패키징과 실리콘 사이의 경계를 모호하게 만드는 새로운 재료와 프로세스를 확인했습니다. 추가로 10배의 인터커넥트 밀도를 달성할 수 있는 고급 패키징을 포함하여 준모놀리식 칩으로 이어지는 무어의 법칙을 패키지의 1조 개 트랜지스터로 확장하는 여정에서 중요한 다음 단계를 공개합니다. 인텔의 재료 혁신은 또한 단 3원자 두께의 새로운 재료를 사용하여 트랜지스터 스케일링 요구 사항을 충족할 수 있는 실용적인 설계 선택을 식별하여 회사가 RibbonFET 이상으로 스케일링을 계속할 수 있도록 합니다.

인텔, 차세대 3D 패키징을 위한 준모놀리식 칩 출시:

- IEDM 2022에서 발표된 인텔의 최신 하이브리드 본딩 연구는 인텔의 IEDM 2021 연구 발표에 비해 전력 및 성능에 대한 밀도가 10배 더 향상되었음을 보여줍니다.

- 3um 피치로의 지속적인 하이브리드 본딩 스케일링은 모놀리식 시스템 온 칩 연결에서 발견되는 것과 유사한 상호 연결 밀도 및 대역폭을 달성합니다.

인텔은 단일 칩에 더 많은 트랜지스터를 장착하기 위해 초박형 '2D' 재료를 찾고 있습니다.

- Intel은 3원자 두께의 2D 채널 재료를 사용하여 게이트 전체에 적층된 나노시트 구조를 시연했으며, 실온에서 낮은 누설 전류로 이중 게이트 구조에서 거의 이상적인 트랜지스터 스위칭을 달성했습니다. 이들은 GAA 트랜지스터를 적층하고 실리콘의 근본적인 한계를 뛰어넘는 데 필요한 두 가지 주요 돌파구입니다.

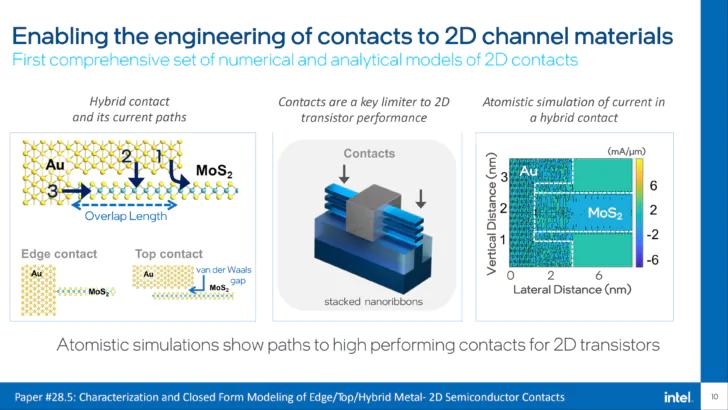

- 연구원들은 또한 고성능 및 확장 가능한 트랜지스터 채널을 위한 길을 더 열 수 있는 2D 재료에 대한 전기 접촉 토폴로지의 최초의 포괄적인 분석을 공개했습니다.

인텔은 고성능 컴퓨팅을 위한 에너지 효율성 및 메모리의 새로운 가능성을 제공합니다.

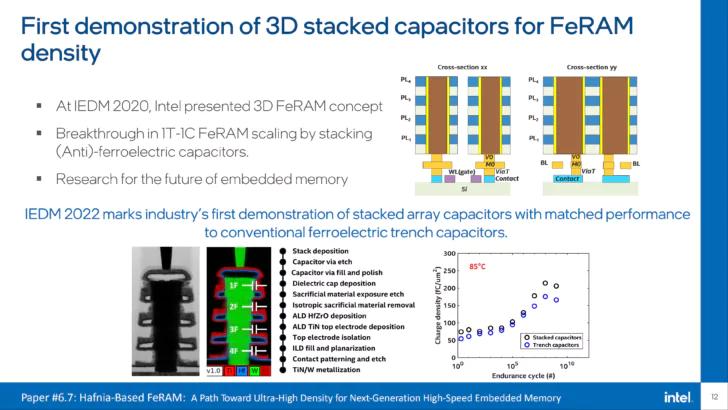

- 칩 영역을 보다 효과적으로 사용하기 위해 인텔은 트랜지스터 위에 수직으로 배치할 수 있는 메모리를 개발하여 스케일링을 재정의합니다. 업계 최초로 인텔은 기존 강유전체 트렌치 커패시터의 성능과 일치하고 로직 다이에 FeRAM을 구축하는 데 사용할 수 있는 스택형 강유전체 커패시터를 시연합니다.

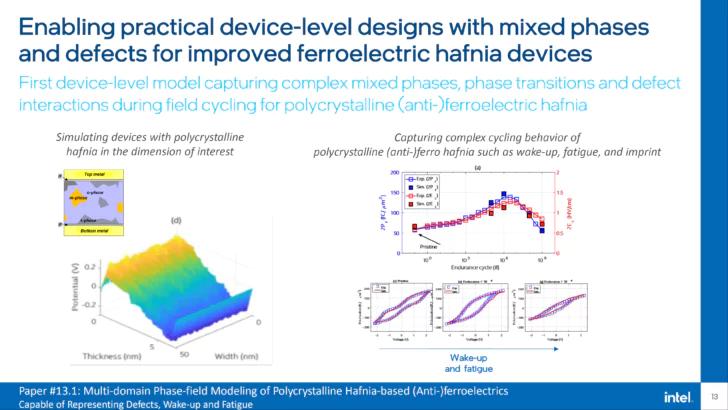

- 업계 최초의 장치 수준 모델은 개선된 강유전성 하프니아 장치에 대한 혼합 단계 및 결함을 캡처하여 새로운 메모리 및 강유전성 트랜지스터를 개발하기 위한 산업 도구를 지원하는 인텔의 상당한 진전을 나타냅니다.

- 인텔은 5G를 넘어 전환하고 전력 효율성 문제를 해결하는 데 한 걸음 더 가까이 다가가기 위해 300mm GaN-on-silicon 웨이퍼에 대한 실행 가능한 경로를 구축하고 있습니다. 이 분야에서 인텔의 혁신은 업계 표준 GaN보다 20배 향상되었으며 고성능 전력 공급에 대한 업계 기록적인 성능 지수를 설정합니다.

- 인텔은 전원이 꺼진 상태에서도 데이터를 유지하기 위해 초 에너지 효율적인 기술, 특히 잊지 않는 트랜지스터에서 획기적인 발전을 이루고 있습니다. 이미 인텔 연구원들은 기술이 실온에서 완전히 실행 가능하고 작동하지 못하도록 하는 세 가지 장벽 중 두 가지를 허물었습니다.

인텔은 양자 컴퓨팅을 위한 더 나은 큐비트를 제공하는 혁신과 함께 물리학의 새로운 개념을 계속해서 도입하고 있습니다.