TSMC의 1nm는 중요한 진전을 이루었습니다 : 실리콘 칩의 물리적 한계를 해결할 수 있습니다.

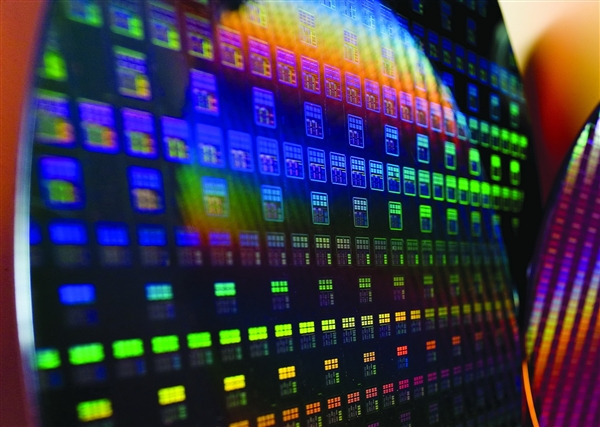

얼마 전 IBM은 매우 흥미로운 2nm 기술 경로를 발표했습니다. 무어의 법칙의 속도는 느려졌지만 실리콘 웨이퍼 축소에 대한 전망은 여전히 넓습니다.

그러나 2nm가 1.5nm와 1nm가 지나면 실리콘 웨이퍼는 물리적 한계에 도달했습니다.

며칠 전 National Taiwan University, TSMC, MIT는 공동 연구 결과를 발표했으며 처음으로 2 차원 물질 접촉 전극으로 semi-metal Bi를 사용하는 것을 제안했습니다. 저항을 크게 줄이고 전류를 증가시켜 실리콘 재료에 필적하는 성능을 만들어 반도체 산업이 다음 1 나노 미터 세대의 과제에 대처하는 데 도움이 될 것입니다.

이 논문은 실리콘 기반 반도체가 이제 5nm 및 3nm로 발전했으며 단위 면적당 트랜지스터 수가 실리콘 재료의 물리적 한계에 근접하고 있으며 성능은 해마다 크게 향상 될 수 없다고 썼습니다. 이전에는 2 차원 재료가 업계에서 높은 기대치를 가지고 있었지만 항상 높은 저항과 낮은 전류와 같은 문제로 인해 제약을 받았습니다.

이 3 자 협력에서 MIT는 반 금속 비스무트 전극의 발견 자이고 TSMC는 비스무트 (Bi) 증착 공정을 최적화했으며 국립 대만 대학 팀은 헬륨 이온 빔 리소그래피 시스템을 사용하여 구성 요소 채널을 나노 크기로 성공적으로 좁혔습니다. 드디어 완성되었고 1 년 반 정도 걸렸습니다.

4 월 말 TSMC는 자사의 4 나노 공정 칩이 2021 년 말 '위험 생산'단계에 진입하여 2022 년 양산을 달성 할 것이라고 말하면서 공정 기술 로드맵을 업데이트했습니다. 3 나노 제품은 출시 될 예정입니다. 2 나노 미터 공정이 개발 중입니다.